PROJECT Goals

1. Development of a FPGA

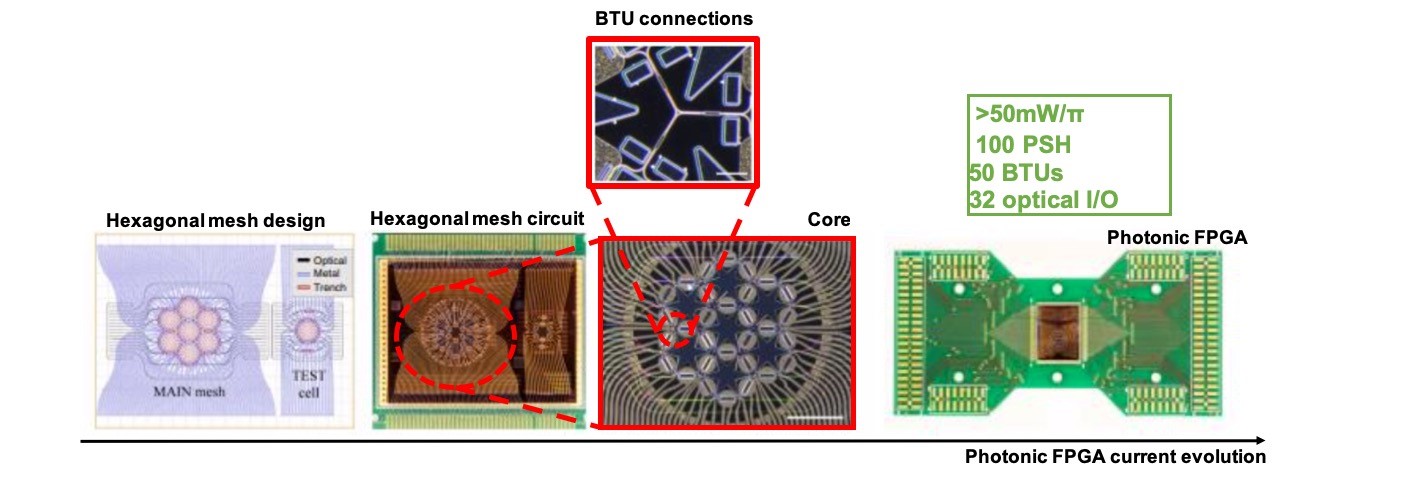

NEoteRIC proposes the photonic development of a field programmable gate array (FPGA). The technological evolution of photonic FPGA technology within NEoteRIC will provide a multiplicative effect in the number of integrated units (4 times improvement), in the number of available I/O (2 times improvement) and a reduction of power consumption (5 times improvement). This advantage will render the scheme superior compared to previous photonic neuromorphic approaches in terms of node number, power consumption and operational bandwidth.

2. Preserve photonics advantages with less energy

NEoteRIC’s BTO enhanced photonic FPGAs will preserve and enhance the advantages of the first generation of photonic FPGAs and additionally will unleash the potential for four orders of magnitude decrease in the energy consumption per unit, nanosecond reconfiguration capabilities and negligible power consumption per operation through BTO phase shifters. This feature will render NEoteRIC’s proposition superior to all processing electronic/photonic counterparts in terms of operational bandwidth/power consumption.

3. Create a disruptive generation of neuromorphic photonic chips

NEoteRIC aims to merge cutting edge photonic technologies like reconfigurable silicon integrated structures and planar ferroelectric schemes so as to spawn a disruptive generation of general purpose neuromorphic photonic chips, having hundreds of nodes, exhibiting supreme processing speed and consuming negligible power. Low-power & high-speed chip reconfiguration will unleash the true potentials of NEoteRIC’s arsenal providing for the first time photonic implementation of cutting edge neuromorphic paradigms, multi-task capabilities and on-chip.

4. A platform for implementing machine learning paradigms directly in the optical domain

The generation of a high-performance photonic FPGA PICs will offer a proliferating platform for implementing a series of state-of-the-art machine learning paradigms directly in the optical domain, whereas the ability of photonic chips to be reconfigured will enable the ability to switch among neural architectures in high-speed, thus tackling multiple-tasks in a parallel manner, and provide the ability to process multi-GHz inputs with marginal energy consumption.

5. Alleviate the need of offline training

A major milestone that will be addressed in the context of NEoteRIC is the implementation of training techniques directly on-chip alleviating the need for offline training. This feature will be delivered through the low-power reconfiguration capabilities of the photonic FPGA. NEoteRIC’s objective is to investigate and implement cutting edge training schemes such as Brute-force computation of gradient, Adjoint variable method and Nonlinearity Inversion.

6. More speed minimizing power consumption

Through NEoteRIC’s photonic-FPGA a neuromorphic platform cytometric data analysis will be performed in the analogue-optical domain, alleviating the need for high-speed electronics, offering unparalleled speed, eliminating offline data storage and minimizing power consumption due to photonic passive processing. NEoteRIC’s devices can be directly implemented in a vast pallet of applications ranging from laser manufacturing to cyber security applications.